この記事ではPLCソフト設計で各工程の構造をルール化するメリットとその具体例について解説していきます。

目次

”各工程の構造のルール化”とは

結論としまして、「異常・工程・出力・各種工程間ハンドシェイクなどの順番をルール化した後に、それらを掘り下げて中身の構造をルール化すること」ことです。

ラダーを書いていく順番やアドレスが決まれば、次は具体的に中身の構造を決めていきます。

もうすでに会社で決まっていたり、MYルール定めてらっしゃる場合は、それを無理に変える必要はないと思います。今回は私の方で実践している内容についてお伝えしたいと思います。絶対的な決まりはありませんので、考え方の内の1つとして捉えて頂ければOKです。

なぜ構造をルール化するのか

構成の順序がルール化され、アドレスも決めていきました。最後に中身を整えていきます。この中身が最後に重要になってくる部分です。

ルール化することで、設計時間が短縮出来たり、再発防止策を盛り込んでルール化することで過去に経験したトラブルを未然に防ぐことが出来ますとお伝えしてきました。

この章の各工程の構造をルール化する理由も、Q(品質)・C(コスト)・D(納期)の改善が最終の目的ですのでコメントやアドレスをるルール化させる理由と共通になってきます。

特に申し上げたい内容としましては

①構造が決まっていると、最後にラダー全体が統一できる

②直観で流れをつかむことが出来る

③設計時間短縮につながる

この辺りになります。もう少し具体的に説明していきます。

構造が決まっていると、最後にラダー全体が統一できる

例えば全体の流れを「異常・工程歩進・計算・出力・各種工程間ハンドシェイクなど」で定義してルール化している場合、中身もその流れに合わせて作成する必要が出てくる場合が多いです。

例えば「異常」に焦点を当ててさらに流れを決めていくとすると、私の場合は

①エラー発生ON/OFFビット作成

②非常停止異常(要電断)とそれ以外に分ける

③工程別に作成する

④異常無しのフラグを作成する

この順序で毎回ブレなく作っています。後ほど実際にラダーと合わせて説明します。

ラダー全体が統一できて、詳細の流れも決めておけば第三者への引継ぎ時も流れが分かるのでスムーズにいきますし、時間短縮にもつながります。

また、失敗事例をフィードバックして展開しておくと不具合も標準化されずに済みます。

直観で流れをつかむことが出来る

これも実はコメントの所でお伝えした内容なのですが、"直感"ではなく直観です。本来”直観”は直接的に本質を捉える意味で使われます。

ここでは私として、"直感"と”直観”を足して2で割る感覚で考えています。瞬間的に感覚でかつ本質を捉える。いわばイメージングするような意味です。

ルール化された流れを理解していると、読むうちに次の手が分かるようになってきます。ラダーを読む=本を読み理解する事と同じことであると私は考えています。ゆわばその会社独自のラダー速読術を取得するみたいなものだと思います。

仮に引継ぎ後に問題があっても、ラダー起因であれば推測が付きやすくなるので不具合箇所のヤマが張れるようになります。ここは経験も伴いますので実践で鍛えるしかありませんが経験を積めば確実に伸びます。

ただ不具合全てがそのヤマ通りである事は基本的に少ないですが、そこからの派生もわかってくるようになるので、結果的にトラブル対応の時間短縮にもつながります。

設計時間短縮につながる

先走って説明してしまいましたが、読み手が流れを理解していれば引継ぎの時も一から構造を説明しなくて済みますし、ルールに沿って進めるので、新しい線路を一から引き直さなくてOKなので、結果として時間の短縮につながります。

どのように構造をルール化するか

それでは先ほど少し触れましたが、「異常」の構造について説明していきます。

流れとしましては

①エラー発生ON/OFFビット作成

②非常停止異常(要電断)とそれ以外に分ける

③工程別に作成する

④異常無しのフラグを作成する

この順序になります。早速これらをラダーに起こした場合を紹介していきます。

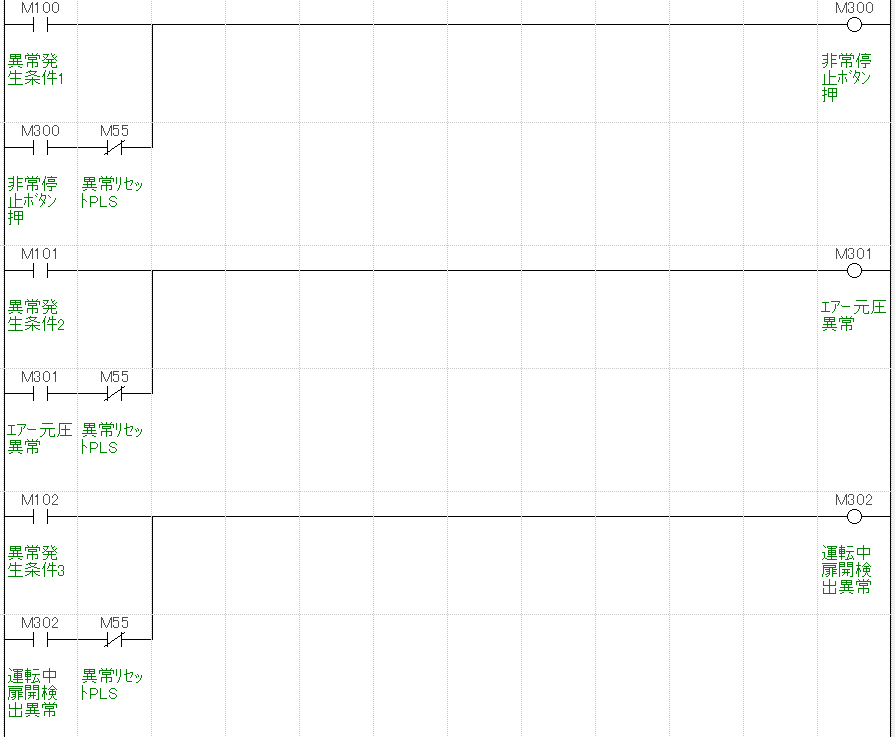

エラー発生ON/OFFビット作成

最初にエラーを発生させるビットを作成します。今回は自己保持回路で組んでいます。

それぞれ

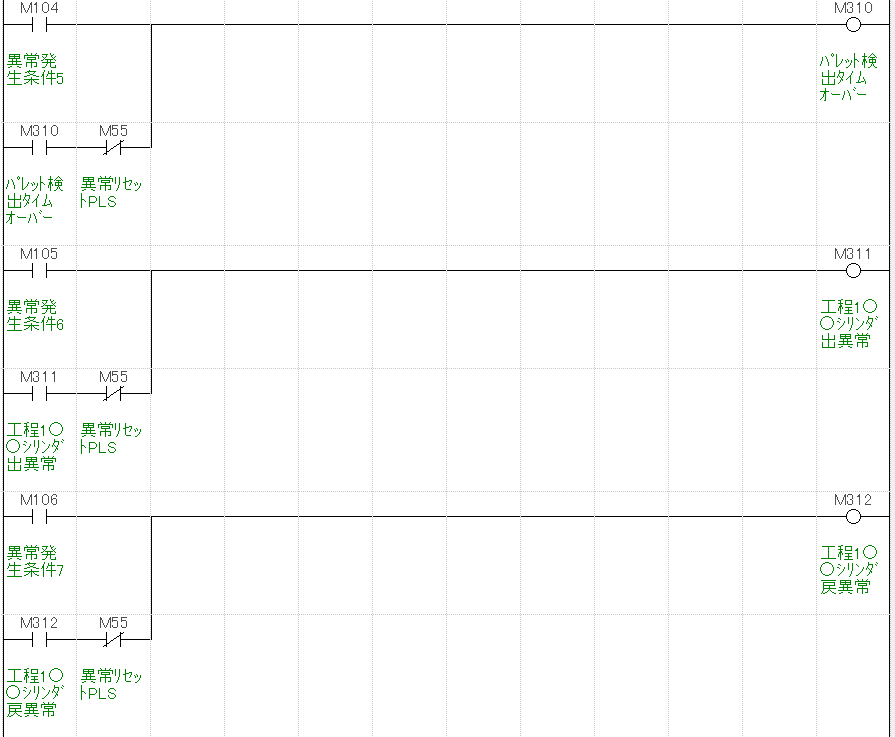

①M100~M108:エラーを発報する時の条件として仮に設定したものです

②M55:リセット指令が入った際にビットをOFFさせるための部分です。

③M300~M321:エラー発生ビット

とします。

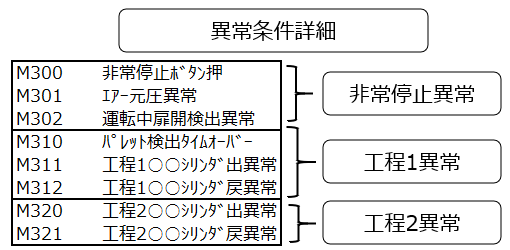

非常停止異常(要電断)とそれ以外に分ける

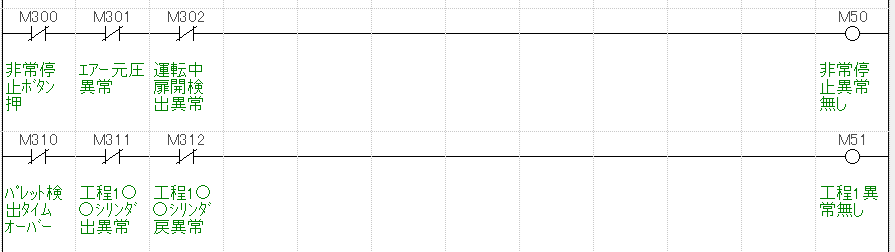

まずM300~M321のエラー発生ビットは非常停止異常(要電断)とそれ以外に分けます。

今回は例として、非常停止異常と工程1、工程2に分けました。

工程別に作成する

先ほど例として、非常停止異常と工程1、工程2に分けました。

次に各工程に起因するエラーでまとめていきます。ラダーを実際に書いていきます。

※異常発生条件がONの状態ですと、異常リセットしてもエラー発生ビットはONの状態となります。

非常停止異常の部分

工程1で発生するエラー

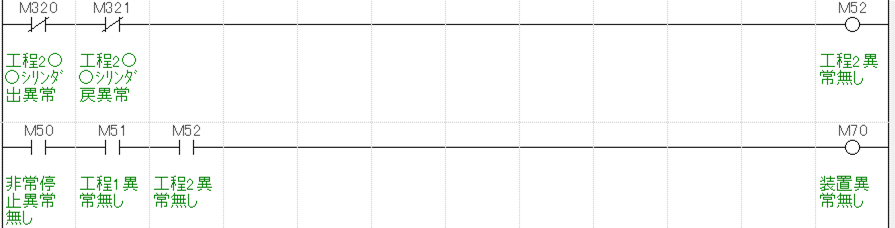

工程2で発生するエラー

ここまでがエラー発生ビットを制御する部分です。

次にこれらのエラー発生ビットを使って、実際に自動運転を行っていいか?手動操作を実施していいか?そのための条件(絶対条件)を作るためにエラー発生ビットをまとめていきます。それが次の「異常無しフラグを作成する」部分になります。

異常無しのフラグを作成する

次に絶対条件を作るためにエラー発生ビットをまとめていきます。

各エラーを非常停止異常や工程に分けて、異常無しフラグを作ります。異常が無いとき(正常時)にONするように作ります。

最後にその異常無しフラグをANDでまとめて「M70:装置異常無し」とします。このM70をそれぞれの操作の絶対条件に使用します。

メモ

M50やM51などで、異常項目が多くなる場合は[= k0 k□M300]などに置き換えてもOKです。□には対応するビット数の定数を指定します。k1なら4ビットですね。

装置の異常が無いとき(装置正常時)にONするビット「M70:装置異常無し」を作成しましたら、次に各インターロックや自動運転の絶対条件に使用します。

このようにルール化して形を作っておけば、その手順のレールに沿って当てはめていくだけなので設計時間の短縮や根本的な不具合の防止につながります。

まとめ

今回の記事を要約するとこんな感じです。

ポイント要約

①構造のルール化とは異常・工程・出力・各種工程間ハンドシェイクなどの順番をルール化した後に、それらを掘り下げて中身の構造をルール化すること

②構造が決まっていると、最後にラダー全体が統一できる

③ルール化することで最終的に時間短縮・不具合の発生防止などQCDの改善に効果がでる